Cell::cellЄЧЅьЅЄЅШЅь

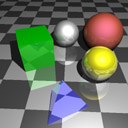

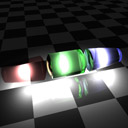

ГиЩєЄЮКЂ(ЄЈЁМЄШЁЂ5,6ЧЏСАЄЧЄЙЄЋ)ЁЂВнТъЄЧКюЄУЄПФЖИХХЕХЊraytracerЄђ

КЃЄЮДФЖЄЫМъФОЄЗЄЗЄЦЁЂ

cygwin @ Core2Duo E6400 (2.13GHz)

linux(fc5) @ Cell 3.2GHz

ЄЧЦАЄЋЄЗЄЦЄпЄПЁЃ

ЅНЁМЅЙЄЯСДЄЏЦБЄИЄЧЁЂ

makeЛўЄЮЅЊЅзЅЗЅчЅѓЄт -O3 -funroll-loops ЄЧЦБЄИЁЃ

bmpЄЧЪнТИЄЙЄыКнЄЫЁЂCellТІЄЌBigEndianЄЪЄЮЄЧЁЂЅаЅЄЅШЅЙЅяЅУЅзЄЗЄЦЄыЄЏЄщЄЄЁЃ

SPEЄЯЛШЄяЄКЁЂPPEЄЮЄпЄЮЛШЭбЁЃ

ЗыВЬЄЯЁЂ

0m06s @ Core2Duo , 0m10s @ Cell

0m06s @ Core2Duo , 0m10s @ Cell

0m23s @ Core2Duo , 0m25s @ Cell

0m23s @ Core2Duo , 0m25s @ Cell

0m21s @ Core2Duo , 0m19s @ Cell

0m21s @ Core2Duo , 0m19s @ Cell

2m20s @ Core2Duo , 1m56s @ Cell

2m20s @ Core2Duo , 1m56s @ Cell

PPEЄЯАеГАЄШТЎЄЄЄЪЁЃ

СДЩєЧмЄЏЄщЄЄКЙЄЌЩеЄЏЄШЛзЄУЄПЄѓЄЧЄЙЄЌЁЂ

УБНуЄЪЅГЁМЅЩЄЪЄЮЄЧЁЂНуПшЄЫЅЏЅэЅУЅЏЄЮЙтЄЕЄЌЗыВЬЄЫНаЄЦЄыЄЮЄЋЄтЁЃ

spuЄЧЄтЄфЄыЄЋЁЊЄШЛзЄУЄПЄѓЄЧЄЙЄБЄЩЁЂЬЕЭ§ЄфЄъЦБЄИЅНЁМЅЙЄђspu-gccЄЫПЉЄяЄЛЄПЄщЁЂ

ЅъЅѓЅЏЛўЄЫ relocation truncated to fit : SPU_ADDR16,SPU_REL16 ЄЌТчЮЬШЏРИЄЗЄЦМКЧдЁЃ

ЄГЄЮЅЈЅщЁМЄЯЁЂЅГЅѓЅбЅЄЅыЛўЄЯСъТаЅИЅуЅѓЅзЄђСлФъЄЗЄЦЄПЄБЄЩЁЂ

ЄЄЄЖЅъЅѓЅЏЄЗЄшЄІЄШЄЗЄПЄщЦЯЄЋЄЪЄЏЄЪЄУЄСЄуЄУЄПЁЂЄДЄсЄѓЁЂ

ЄШЄЄЄІОьЙчЄЫНаЄыЄтЄЮЄШЛзЄУЄЦЄЄЄПЄЮЄЧЄЙЄЌЁЂ

(ЄНЄЮОьЙчЄЯЁЂЅсЅтЅъЅтЅЧЅыЄШЄЋЄђЪбЄЈЄПЄщТчФёФЬЄыЄшЄІЄЫЄЪЄы)

ЄЩЄІЄфЄщSPUЄЮОьЙчЄЯЄГЄьЄЌНаЄыЁс256KBЅЊЁМЅаЁМЄщЄЗЄЄЁЃ

16bitЄЗЄЋЅЂЅЩЅьЅЙЖѕДжЄЪЄЄЄЮЄЋЁЃЄЪЄыЄлЄЩЁЃ

ЄЄЄэЄЄЄэЅщЅЄЅжЅщЅъЄђЅъЅѓЅЏЄЗЄЦЄыЄЗЁЂ

ЬЕУуЄУЄЦЛіЄЯЪЌЄЋЄУЄЦЄПЄЮЄЧЮЩЄЄЄБЄЩЁЂ

ЄфЄУЄбportingЄЙЄыЄЮЬЬХнЄРЄшЄЪЄЂЁЃ

ЅьЅѓЅРЅщЄЮЅГЅЂЄРЄБРкЄъНаЄЛЄаЁЂЄШЄъЄЂЄЈЄКЦАЄЏЄшЄІЄЫЄЪЄыЄШЄЯЛзЄІЄЌЁЂ

ЬЬХнЄРЄЋЄщЄоЄПКЃХйЁЃ

ЄГЄьЁЂЅЂЅыЅДЅъЅКЅрЄђИЄЏЄЗЄЦМуДГЅеЅЇЅЄЅЏДѓЄъЄЫЄЙЄьЄаЁЂ

ТПЪЌ10ЧмЄЏЄщЄЄТЎЄЏЄЪЄыЄЗЁЂ

ЄСЄуЄѓЄШЅйЅЏЅПЅщЅЄЅКЄЗЄЦSPE*6ЛШЄЄРкЄьЄаЁЂ

ЄЕЄщЄЫ10ЧмЄЏЄщЄЄТЎЄЏЄЪЄыЄРЄэЄІЄЋЄщЁЂЗз100ЧмЄЏЄщЄЄЙтТЎЄЫЁФ

ЄЪЄУЄПЄъЄЗЄЪЄЄЄЋЄЪЄЂЁЃ

ЛШЄУЄПЅНЁМЅЙ

kmkz.jp/mtm/lab/raytrace/raytrace-20061212.tar.gz

КЃЄЮДФЖЄЫМъФОЄЗЄЗЄЦЁЂ

cygwin @ Core2Duo E6400 (2.13GHz)

linux(fc5) @ Cell 3.2GHz

ЄЧЦАЄЋЄЗЄЦЄпЄПЁЃ

ЅНЁМЅЙЄЯСДЄЏЦБЄИЄЧЁЂ

makeЛўЄЮЅЊЅзЅЗЅчЅѓЄт -O3 -funroll-loops ЄЧЦБЄИЁЃ

bmpЄЧЪнТИЄЙЄыКнЄЫЁЂCellТІЄЌBigEndianЄЪЄЮЄЧЁЂЅаЅЄЅШЅЙЅяЅУЅзЄЗЄЦЄыЄЏЄщЄЄЁЃ

SPEЄЯЛШЄяЄКЁЂPPEЄЮЄпЄЮЛШЭбЁЃ

ЗыВЬЄЯЁЂ

0m06s @ Core2Duo , 0m10s @ Cell

0m06s @ Core2Duo , 0m10s @ Cell

0m23s @ Core2Duo , 0m25s @ Cell

0m23s @ Core2Duo , 0m25s @ Cell

0m21s @ Core2Duo , 0m19s @ Cell

0m21s @ Core2Duo , 0m19s @ Cell

2m20s @ Core2Duo , 1m56s @ Cell

2m20s @ Core2Duo , 1m56s @ Cell

PPEЄЯАеГАЄШТЎЄЄЄЪЁЃ

СДЩєЧмЄЏЄщЄЄКЙЄЌЩеЄЏЄШЛзЄУЄПЄѓЄЧЄЙЄЌЁЂ

УБНуЄЪЅГЁМЅЩЄЪЄЮЄЧЁЂНуПшЄЫЅЏЅэЅУЅЏЄЮЙтЄЕЄЌЗыВЬЄЫНаЄЦЄыЄЮЄЋЄтЁЃ

spuЄЧЄтЄфЄыЄЋЁЊЄШЛзЄУЄПЄѓЄЧЄЙЄБЄЩЁЂЬЕЭ§ЄфЄъЦБЄИЅНЁМЅЙЄђspu-gccЄЫПЉЄяЄЛЄПЄщЁЂ

ЅъЅѓЅЏЛўЄЫ relocation truncated to fit : SPU_ADDR16,SPU_REL16 ЄЌТчЮЬШЏРИЄЗЄЦМКЧдЁЃ

ЄГЄЮЅЈЅщЁМЄЯЁЂЅГЅѓЅбЅЄЅыЛўЄЯСъТаЅИЅуЅѓЅзЄђСлФъЄЗЄЦЄПЄБЄЩЁЂ

ЄЄЄЖЅъЅѓЅЏЄЗЄшЄІЄШЄЗЄПЄщЦЯЄЋЄЪЄЏЄЪЄУЄСЄуЄУЄПЁЂЄДЄсЄѓЁЂ

ЄШЄЄЄІОьЙчЄЫНаЄыЄтЄЮЄШЛзЄУЄЦЄЄЄПЄЮЄЧЄЙЄЌЁЂ

(ЄНЄЮОьЙчЄЯЁЂЅсЅтЅъЅтЅЧЅыЄШЄЋЄђЪбЄЈЄПЄщТчФёФЬЄыЄшЄІЄЫЄЪЄы)

ЄЩЄІЄфЄщSPUЄЮОьЙчЄЯЄГЄьЄЌНаЄыЁс256KBЅЊЁМЅаЁМЄщЄЗЄЄЁЃ

16bitЄЗЄЋЅЂЅЩЅьЅЙЖѕДжЄЪЄЄЄЮЄЋЁЃЄЪЄыЄлЄЩЁЃ

ЄЄЄэЄЄЄэЅщЅЄЅжЅщЅъЄђЅъЅѓЅЏЄЗЄЦЄыЄЗЁЂ

ЬЕУуЄУЄЦЛіЄЯЪЌЄЋЄУЄЦЄПЄЮЄЧЮЩЄЄЄБЄЩЁЂ

ЄфЄУЄбportingЄЙЄыЄЮЬЬХнЄРЄшЄЪЄЂЁЃ

ЅьЅѓЅРЅщЄЮЅГЅЂЄРЄБРкЄъНаЄЛЄаЁЂЄШЄъЄЂЄЈЄКЦАЄЏЄшЄІЄЫЄЪЄыЄШЄЯЛзЄІЄЌЁЂ

ЬЬХнЄРЄЋЄщЄоЄПКЃХйЁЃ

ЄГЄьЁЂЅЂЅыЅДЅъЅКЅрЄђИЄЏЄЗЄЦМуДГЅеЅЇЅЄЅЏДѓЄъЄЫЄЙЄьЄаЁЂ

ТПЪЌ10ЧмЄЏЄщЄЄТЎЄЏЄЪЄыЄЗЁЂ

ЄСЄуЄѓЄШЅйЅЏЅПЅщЅЄЅКЄЗЄЦSPE*6ЛШЄЄРкЄьЄаЁЂ

ЄЕЄщЄЫ10ЧмЄЏЄщЄЄТЎЄЏЄЪЄыЄРЄэЄІЄЋЄщЁЂЗз100ЧмЄЏЄщЄЄЙтТЎЄЫЁФ

ЄЪЄУЄПЄъЄЗЄЪЄЄЄЋЄЪЄЂЁЃ

ЛШЄУЄПЅНЁМЅЙ

kmkz.jp/mtm/lab/raytrace/raytrace-20061212.tar.gz